|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Industr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 |

| System Lev                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 |

| Industry Counc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6 |

| AMAZING Microelectronic Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| amui Danalo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| Barth Electronics The Makes record their State S |   |

| <b>∼ em</b> test FLEXT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| HISILICON IBM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| Littelfuse°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| Microsoft NeX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| ORACLE PRAGMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| <b>QPX</b> Qualcon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| SAMSUNG SEMTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| socionext sorics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

# Industry Survey Report stem Level – Direct PIN ESD

Industry Council on ESD Target Levels

Graz

February 2025

10 Revision 1.0

11

7

8

| 12 |                                                                            |

|----|----------------------------------------------------------------------------|

| 13 | This document is available through various public domains as listed below: |

| 14 |                                                                            |

| 15 | The Industry Council on ESD                                                |

| 16 | http://www.esdindustrycouncil.org/ic/en/                                   |

| 17 |                                                                            |

| 18 | The Electrostatic Discharge Association                                    |

| 19 | http://www.esda.org/                                                       |

| 20 |                                                                            |

| 21 |                                                                            |

| 22 |                                                                            |

#### Abstract

- The read-out report addresses the feedback of the industry wide survey on system level direct pin ESD performed in the time frame of April to August 2024.

- The focus is on the status in industry and no recommendations are provided.

- The survey results show the usage of system level direct pin ESD in many application domains.

- It also highlights the lack of an aligned test procedure and target levels.

## **About the Industry Council on ESD Target Levels**

The Council was initiated in 2006 after several major U.S., European, and Asian semiconductor companies joined to determine and recommend ESD target levels. The Council now consists of representatives from active full member companies and numerous associate members from various support companies. The total membership represents IC suppliers, contract manufacturers (CMs), electronic system manufacturers, OEMs, ESD tester manufacturers, ESD consultants and ESD IP companies. In terms of semiconductor market leaders 12 of the top 20 companies are members of the council.

| Core Members                       | Core Members                  |

|------------------------------------|-------------------------------|

| Ashok Alagappan, Ansys             | Tom Meuse, Thermofisher       |

| Robert Ashton, IEEE                | Yasuyuki Morishita, Renesas   |

| Andrea Boroni, STMicroelectronics  | Mototsugu Okushima, Renesas   |

| Brett Carn, Intel                  | David Pommerenke, TU Graz     |

| Kuo-Ji Chen, TSMC                  | Alan Righter, formerly Analog |

| Ann Concannon, Texas Instruments   | Theo Smedes, NXP              |

| Jeff Dunnihoo, Pragma Design       | Andrew Spray, Synaptics       |

| Charvaka Duvvury, iT2 Technologies |                               |

| Co-chair Industry Council          | Teruo Suzuki, Socionext       |

| David Eppes, AMD                   | Mark Styduhar, Marvell        |

| Robert Gauthier, Globalfoundries   | Pasi Tamminen, Danfoss        |

| Reinhold Gaertner, Infineon        | Peter Turlo, Onsemi           |

| Harald Gossner, Intel              |                               |

| Co-chair Industry Council          | Jim Vinson, Renesas           |

| Steffen Holland, Nexperia          | Scott Ward, Texas Instruments |

| Masamitsu Honda, IPL         | Terry Welsher, Dangelmayer |

|------------------------------|----------------------------|

| Brian Hulse, Marvell         | Joost Willemen, Infineon   |

| Chanhee Jeon, Samsung        |                            |

| David Klein, pSemi           |                            |

| Florian Klotz, Intel         |                            |

| Peter Koeppen, Esdunlimited  |                            |

| Hiroyasu Ishizuka, Maxwell   |                            |

| Satoshi Isofuku, TET         |                            |

| Reza Jalilizeinali, Qualcomm |                            |

| Peter de Jong, Synopsys      |                            |

| James Karg, AMD              |                            |

| John Kinnear, IBM            |                            |

| Hans Kunz, Texas Instruments |                            |

| Jam-Wam Lee, TSMC            |                            |

| Tim Maloney, SBC Global      |                            |

|                              |                            |

| Associate Members                          | Associate Members                   |

|--------------------------------------------|-------------------------------------|

| Efraim Aharoni, Tower Semiconductor        | Markus Mergens, Nexperia            |

| Philip Baltar, IDT                         | Greg O'Sullivan, Micron             |

| John Brodsky, Texas Instruments            | Christian Russ, Infineon            |

| Mike Chaine, Micron                        | Ryan Hsin-Chin Jiang, Amazing IC    |

| Graver Chang, ma-tek                       | Jörg Schreiter, Racyics             |

| CJ Chao, Richwave                          | Vrashank Shukla, Texas Instruments  |

| Bernard Chin, Qorvo                        | Marko Simicic, IMEC                 |

| Che-Hao Chuang, Amazing IC                 | Gaurav Singh, Renesas               |

| J Colby, Littelfuse                        | Jeremy Smith, Electrostatics        |

| Ted Dangelmayer, Dangelmayer               | Arnold Steinman, independent expert |

| Tom Diep, Texas Instruments                | Isabel Stumfall, Semtech            |

| Sreeker Dundigal, Qualcomm                 | Nobuyuki Wakai, Toshiba             |

| Kai Esmark, Infineon                       | J Winstead, Qualcomm                |

| Rita Fung, Cisco                           | Heinrich Wolf, Fraunhofer EMFT      |

| Howard Ga, SMIC Semiconductor              | Xiong Ying, Huawei                  |

| Morphy Gao, Hisilicon                      | Joshua Yoo, Core Insight            |

| Horst Gieser, Fraunhofer EMFT              | MyoungJu.Yun, Amkor                 |

| Mike Heaney, independent expert            | Kun-Hsien Lin, Amazing IC           |

| Leo G. Henry, ESD-TLP Consultants          | Frederic Lafon, Valeo               |

| Stevan G Hunter, independent expert        | Henning Lohmeyer, Bosch             |

| Marty Johnson, independent expert          | M Lee, Semtech                      |

| Melissa Jolliff, NASA                      |                                     |

| Ming-Dou Ker, NYCU                         |                                     |

| Chang Kim, Samsung                         |                                     |

| Hangu Kim, Samsung Institute of Technology |                                     |

| Jaehyok Ko, Samsung                        |                                     |

| Marcus Koh, Everfeed                       |                                     |

| Kitae Lee, Samsung                         |                                     |

| ·                                          |                                     |

| David Swenson, Affinity Static Control Consulting |  |

|---------------------------------------------------|--|

|                                                   |  |

**Acknowledgments:** The Industry Council would like to thank all respondents to the survey and the authors, reviewers, and specialists who shared a great deal of their expertise, time, and dedication to complete this document. **Editor:** Florian Klotz, Intel **Working Group Chair:** Harald Gossner, Intel **Authors:** Jeffrey Dunihoo, Pragma Design David Eppes, AMD David Pommerenke, TU Graz Robert Ashton, ESD Association Tom Meuse, ThermoFisher David Klein, pSemi Charvaka Duvvury, iT2 Technologies Peyman Ensaf, Intel

#### **Mission Statement**

The Industry Council on ESD Target Levels was founded on its original mission to review the ESD robustness requirements of modern IC products to allow safe handling and mounting in an ESD protected area. While accommodating both the capability of the manufacturing sites and the constraints posed by downscaled process technologies on practical protection designs, the Council provides a consolidated recommendation for future ESD target levels. The Council Members and Associates promote these recommended targets for adoption as company goals. Being an independent institution, the Council presents the results and supportive data to all interested standardization bodies.

In response to the growing prevalence of system level ESD and EOS issues, the Council has now expanded its mission to directly address one of the most critical underlying problems: insufficient communication and coordination between system designers (OEMs) and their IC providers. A key goal is to demonstrate and widely communicate that future success in building ESD robust systems will depend on adopting a consolidated approach to system design based on a clear and quantitative understanding of the IC robustness. To ensure a broad range of perspectives the Council has expanded its roster of Members and Associates to include OEMs as well as experts in system design and test.

#### **Preface**

- The presented report is a summary of the findings of an industry wide survey on system level direct pin ESD (SL-DPE) which was performed by Industry Council on ESD Target Levels in the time frame from April

- 91 to August 2024. The summary only targets the information about the industry feedback and doesn't

- 92 imply any recommendation for test concepts or target levels.

#### **Disclaimers** 94 95 96 The Industry Council on ESD Target Levels is not affiliated with any standardization body and is not a 97 working group associated with JEDEC, ESDA, JEITA, IEC, or AEC. 98 99 This document was compiled by recognized ESD experts from numerous semiconductor supplier companies, contract manufacturers and OEMs. The data represents information collected for the specific 100 101 analysis presented here; no specific components or systems are identified. 102 103 The Industry Council, while providing this information, does not assume any liability or obligations for 104 parties who do not follow proper ESD control measures.

# **Table of Contents**

123

| 108 | Glossary                       | of Terms                                             | 11 |  |

|-----|--------------------------------|------------------------------------------------------|----|--|

| 109 | Executive Summary              |                                                      |    |  |

| 110 | Introduct                      | ion                                                  | 12 |  |

| 111 | 1.1                            | System Level Direct Pin ESD (SL-DPE) industry survey | 12 |  |

| 112 | 1.2                            | Survey Setup                                         | 12 |  |

| 113 | 1.3                            | Participation                                        | 13 |  |

| 114 | Chapter 1: Real World Failures |                                                      |    |  |

| 115 | Chapter 2: Lab Testing         |                                                      |    |  |

| 116 | Chapter 3                      | 3: Qualification/Testing Targets and Design Goals    | 25 |  |

| 117 | Summary                        | and Outlook                                          | 33 |  |

| 118 | Appendix                       | A:                                                   | 34 |  |

| 119 | A.1 Questionnaire              |                                                      |    |  |

| 120 | A.2 De                         | tailed responses to text questions                   | 41 |  |

| 121 |                                |                                                      |    |  |

| 122 |                                |                                                      |    |  |

# **Glossary of Terms**

124 125 126 **CDM Charged Device Model** 127 **EMC** ElectroMagnetic Compatibility 128 **EFT Electrical Fast Transient** 129 **ESD** ElectroStatic Discharge 130 EOS **Electrical OverStress** 131 **HMM Human Metal Model** 132 HBM **Human Body Model** 133 **PESD** Powered ESD 134 SL System Level 135 SL-DPE System Level - Direct Pin ESD 136 TLP Transmission Line Pulsing 137 138 139 140 141 142 143

# **Executive Summary**

144

145

151

152

153

154

155

156

157

146 The system level direct pin ESD survey has targeted the usage of stress pulses directly to system or 147 subsystem pins of a system port (like USB). 54 responses have been received spreading across various 148 industries including IC suppliers and IC (end)customers and geographies. Real-world failures are reported 149 by 2/3 of the respondents. The predominant location for real world failures is at the customer site. A diverse spectrum of failure scenarios is observed. 150

System Level testing is most often done using IEC 61000-4-2 generators. Human metal model dominates the type of scenario to be reproduced (in contrast to cable discharge). The stress testing is very often a customer demand. The levels range from 2kV (or lower) to 15 kV without TVS and from 4 kV to > 15kV with TVS for almost all pin types which connect to a system pin. About 40% of the responses are reporting correlation between tested robustness and field returns. If correlation is not evident, it is mostly attributed to insufficient statistics and lack of information. 2/3 of the responses are considering SL-DPE as a design criterion. The design decisions are predominantly based on TLP results.

# Introduction

# 1.1 System Level Direct Pin ESD (SL-DPE) industry survey

- The term SL-DPE is coined for the stress testing of system port pins like a USB connector of a notebook computer by directly applying a type of ESD stress to one exposed pin of the connector. In most cases IEC 61000-4-2 ESD generators are used for this purpose. While the IEC 61000-4-2 standard itself excludes this type of stress testing if the connector has a grounded shield, this is, nevertheless, widely applied to characterize the robustness of a system interface. Due to the missing standard test practice and common protection design goals, there is often a misunderstanding and misalignment between IC supplier and system designer.

- 170 To get an overview of the usage across various industries and types of interfaces as well as the ways of

- testing and applied target levels, an industry-wide survey was conducted by the Industry Council on ESD

- 172 Target Levels. The intention of this report is to give a comprehensive readout of the survey. At this point,

- it is not intended to be a white paper giving recommendations or proposing guidelines.

# 1.2 Survey Setup

- The industry survey was designed by the working group for System Level Direct Pin ESD (SL-DPE) of the Industry Council on ESD Target Levels. The answers were collected using Microsoft Forms and responses were recorded anonymously. The survey was launched at the end of April 2024 and was open until the end of August 2024.

- A total of 32 questions were asked, either single-choice, multiple-choice, or text-based. The questionnaire could be completed leaving any number of questions unanswered. Answers left blank were ignored for the analysis. The percentages provided below are referring to how often a particular answer was given/selected as compared to total replies to a question note, that for questions allowing to select multiple possible answers, the percentages of the individual answers are, hence, not adding up to 100. For reference, the full set of questions for the survey is shown in Appendix A1. Some of the answers given in text form have been paraphrased, and/or similar ones combined for the data presented.

- The questions and the corresponding responses can be organized into three categories: (1) real world failures (2), lab testing (3), targets & design. The report will follow this structure.

# 1.3 Participation

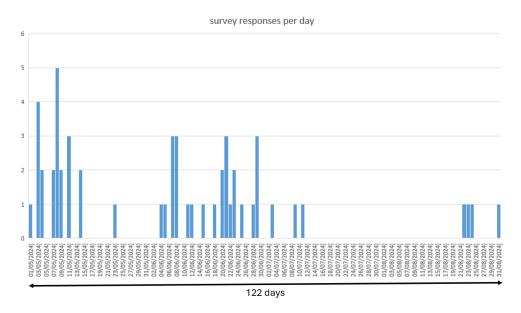

The survey was open from April to August 2024 and during that period a total of **54 responses** were submitted with the following distribution over time:

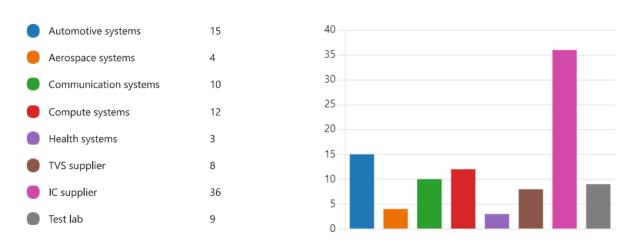

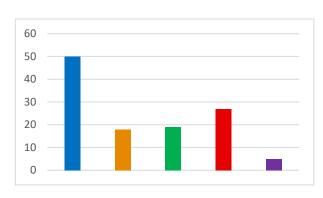

1. [Q01] Which industry or industries do you belong to? (select all that apply)

[Q1] 54 answers have been provided. Responses came from a wide range of industries, with *IC suppliers* being the dominating one. Several respondents identified as belonging to more than one category with one of them even selecting seven different options. Out of the 36 *IC supplier* responses, only 20 identified merely as such while 16 selected further categories as well. For some of the questions below, the responses were also analyzed for *non-IC suppliers* and *IC suppliers* separately, where the latter then refers to all 36 responses mentioning *IC supplier* in question Q01.

# Chapter 1: Real World Failures

206207

208

209

210

211212

213214

215216

217

218

219

220221

222

223224

225

226

227

228

Summary: There were some real-world failures reported, however, their interpretation is not always clear. The breakdown of these responses is examined below.

- ~2/3 have experienced real world failures

- Predominant location for real world failures is at customer site

- Diverse spectrum of failure scenarios with the following mentioned multiple times:

- cable plugging events

- o testing at customer (also to pins with non system level (SL) robustness target)

- o too little information from customer

- 80% conduct failure analysis: mostly on-chip damage (thermal and dielectric breakdown)

## 2. [Q02] Have you experienced real world failures at port pins?

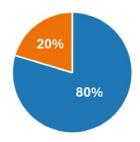

[Q02] 53 answers have been provided. ~2/3 report that they have experienced real world failures at port pins. It should be noted that the term 'real world' was not further defined in the questionnaire and might carry different meanings for responders with different backgrounds. For IC manufacturers, it may refer to the company using the IC, which may be doing some EMC testing. For system designers, however, it may refer to the end customer. Comparing responses for *IC suppliers* vs. *non-IC suppliers*, shows a reported field failure rate of 61% and 71%, respectively.

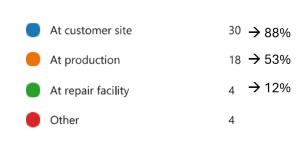

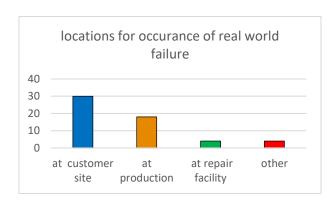

3. [Q03] Where have real world failures occurred? (select all that apply)

229 230 231

232

233

234

235 236

237

238

239

240 241

242 243

244 245

246

247

248

249

250 251

252 253 254

255 256 For 'Other', the following answers were given

- Certification lab

- At customer site, however, very little information is given back to us from our customers. Thus, the details of the failures are not there

- At customer system tests

- At IC customer site when doing testing or prototyping system

[Q03] 34 answers have been provided, aligning with the responses in the previous question Q02. Out of these, 88% reported the customer site as the location where real-world failures occur, followed by at production with 53%. For these two locations there is no notable difference between IC suppliers and non-IC suppliers. However, only non-IC suppliers report failures at repair facilities. 3/4 written responses for others could also be considered in the customer site category, further underlining it as the most common location for real world failures.

4. [Q04] Can you describe the real world failure scenario with a few words?

for detailed responses, see [Q04] in Appendix A2

[Q04] 32 answers have been provided. Overall, a broad spectrum of responses was provided describing scenarios at different levels of detail and scope. Two recurring trends were referring to cable plugging events as well as testing at customer sites. Also, there is frequent mention of insufficient availability of information from the customer.

## 5. [Q05] Do you do failure analysis?

[Q05] 53 answers have been provided. 42 out of these state that they conduct some sort of failure analysis. Notably, this is more than the 34 which responded in Q02 that they have experienced real world failures at port pins. In fact, 11 responses (9 out of them being *IC suppliers*) which selected *no* in Q02 did select *yes* for Q05 and only 3 that encountered failures according to Q02 do not carry out failure analysis. The reason for this mismatch is not clear but could be due to failures occurring during in-house testing before product release but after product release there were no field failures. However, it indicates that the prevalence of failures is even higher than reported in Q02.

6. [Q06] Can you describe the type of failure (thermal, dielectric breakdown,...) and the failure location (TVS diode, on board resistor,, on chip metal, input or output transistor,...)?

for detailed responses, see [Q06] in Appendix A2

[Q06] 37 responses have been provided. Several failure types are described in the written responses, the two predominant ones being *dielectric breakdown* (15x) and *thermal damage* (22x). Most of the failures are reported to be on die and only a few (5x) are mentioning damage at board level. While many replies do not give details on the impacted structures, there are several mentioning damage of ESD components (11x) as well as one of insufficient ESD protection due to cost and performance. Notably, there is very little reporting of *soft fails* with only two mentions.

# Chapter 2: Lab Testing

282 **Summary:**

280 281

283

284

285

286

287

288

289

290

291

- Most laboratories reported that Pin testing uses the IEC 61000-4-2 or closely related generators.

- Human metal model dominates the type of scenario to be reproduced (in contrast to cable discharge)

- To access the pins a wide variety of connection methods is used, from small pins to breakout boards and cables.

- The demand by a majority of customers justifies the need for SL-DPE

7. [Q07] Who is requiring System Level Direct PIN ESD (SL-DPE)? (select all that apply)

292

293

294

295296

297

298

299

For 'Other', the following answers were given:

- Need to be competitive with other vendors

- Would be good internal qualification control

- External qualification

- IEC documents for ICs (EMC context)

- Replicating Field Failures

- Industry standards for specific IC type/market;

- Nobody is requiring it (2x)

300 301

302

303 304

305

306

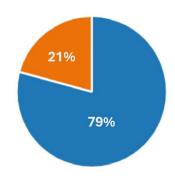

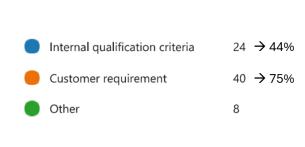

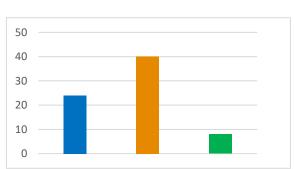

[Q07] We received 54 responses, note that it was possible to select more than one reason.

"Customer requirements" dominated with 75%. For non-IC suppliers, customer requirements still dominated with 67%, while internal qualification criteria rose from 39% (IC suppliers) to 56% (non-IC suppliers). A smaller group of other reasons, ranging from replicating field failures to nobody required it.

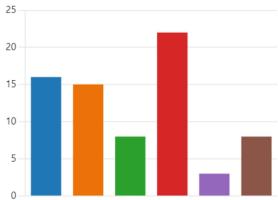

## 8. [Q08] Why do you apply or require SL-DPE? (select all that apply)

For 'Other', the following answers were given

- Customer requirement (5x)

- Sometimes we characterize IC internal protection robustness using TLP

- Mapping of system-level ESD test scenario required by OEM to IC-level setup to support frontloading in overall Tier2 and Tier1 development flow

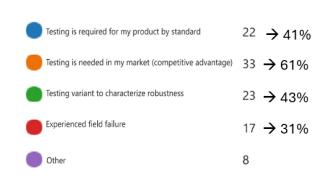

[O08] 54 answers were provided. This question asks for more details about the motivation for SL-DPE testing. The most common motivation, 61%, is to gain a competitive advantage, but requirements and field failures also motivate testing, as well as ensuring quality by testing different variants.

9. [Q09] What stress type do you reproduce or try to reproduce? (select all that apply)

| 323 | For 'Other', the following answers were given                                           |

|-----|-----------------------------------------------------------------------------------------|

| 324 | - IEC 61000-4-2 (3x)                                                                    |

| 325 | - Customer requirement                                                                  |

| 326 | - System level direct discharge (2x)                                                    |

| 327 | - IEC on an IC chip outside system                                                      |

| 328 | - EOS robustness (2x)                                                                   |

| 329 | - Soft Error Immunity                                                                   |

| 330 | - Active ESD directly on pins and stray field effects                                   |

| 331 | - PESD, EFT                                                                             |

| 332 | - Long pulse TLP, IEC gun (IEC could map somewhat to Human Metal ESD but doesn't follow |

| 333 | SP5.6 in fixturing, just apply IEC gun)                                                 |

| 334 | - Unknow rootcause replicated by SL-DPE                                                 |

| 335 | - What is "EOS robustness" supposed to mean?                                            |

| 336 | ••                                                                                      |

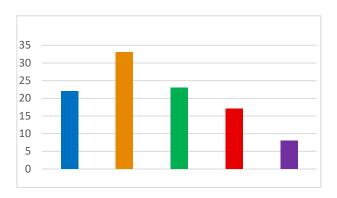

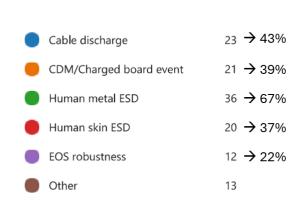

[Q09] 54 answers were given. In these answers we again see the influence of the IEC 61000-4-2 standard: Human metal ESD, the basis for the waveforms in the standard, ranks first with 67%. This is followed by concerns about cable discharge at 43%, CDM and charged board events at 39%. Human skin ESD is usually less severe than human metal ESD. This is reflected in the data: 37% of respondents cited human skin ESD as opposed to 67% who cited human metal ESD.

## 10. [Q10] Which type of pulse generator do you use? (select all that apply)

For 'Other', the following answers were given

- Custom

- Stripline for field coupling

- Field Collapse Pulse (CBE-like)

- Surge

- What is the difference between "IEC 6100-4-2 pulser" and "ISO10605 pulser"?? The pulse is basically exactly the same, you have only the possibility to use also additional RC-network

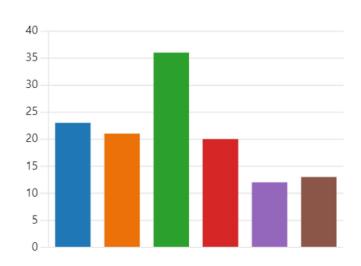

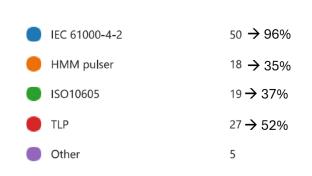

[Q10]. We received 52 responses. The IEC 61000-4-2 ESD generator dominated as the test instrument, with 96% of all responses including this generator. The similar ISO10506 generator is used by 37%, so generators that follow the IEC waveform dominate the choice of test generator, and the similar HMM waveform is used by 35%. The TLP, which produces clean and well reproducible waveforms, is used by 52% and the HMM pulse generator by 35% of the responses.

11. [Q11] Do you use an IEC61000-4-2 table set up (including standard coupling planes, grounding scheme, etc.)?

[Q11] We received 54 responses. The large majority of users of the IEC 61000-4-2 standard (43/50) apply the table set up for the system under test.

12. [Q12] What else do you follow for your setup?

for detailed responses, see [Q12] in Appendix A2

[Q12] 7 answers were provided. This question asks for further details about the test setup or methodology. Seven additional aspects were provided. Two replied that robotic test systems were used and some differences in the grounding of the coupling planes were noted in the survey responses.

13. [Q13] Do you use breakout boards/cables (for example to connect an ESD generator to a USB)?

[Q13] 51 answers have been provided. Breakout boards or cables can greatly change the stress seen by an IC. Within the 51 responses there is a rough split: 43% use breakout boards or cables, while 57% do not. The next questions ask for more details about the breakout boards or cables used. We did not ask why boards or cables were used and we cannot correlate this with the type of pins tested. However, it is reasonable to assume that some pins, such as USB pins, require the use of breakout boards or cables, as the small size of USB, DVI, etc. connectors means that it is not possible to touch connector pins with an ESD generator directly. On the other hand, it is easy to directly access large connector pins, such as those used in car engine controllers.

14. [Q14] Breakout boards - can you please describe?

for detailed responses, see [Q14] in Appendix A2

[Q14] We received 19 other details about breakout boards or cables. Some adapters are just short electrical connections such as "short cable connection", "only lead pin outside", "short cable adapter", "HDMI breakout board with exposed wires/test points", "pogo pin" and more complicated setups such as "evaluation board...", "PCB with minimal set of external components...", "... special PCB for robotic testing..." etc. The influence of the test fixture and the connection from the ESD generator to the system or IC under test can often determine the stress level. This requires further investigation.

15. [Q15] Breakout cables - can you please describe? 403 404 405 for detailed responses, see [Q15] in Appendix A2 406 407 [Q15] 17 answers have been provided. This question goes into more detail about breakout cables. As a wide variety of cables are briefly mentioned, the only conclusion that can be drawn 408 409 level applied. 410 411 412

413

415

416

417

418

419

420

421 422

423

424

425

is that the injection mechanism is uncontrolled, although it can have a strong effect on the stress

16. [Q16] Which discharge mode do you employ in your methodology? (select all that apply)

Air discharge 25 <del>></del> 47%

Contact discharge 53 → 100% 414

> [Q16] We received 53 responses. All respondents use the contact mode and 47% also use the air discharge mode. Contact discharge includes IEC testing as well as alternatives like HMM.

17. [Q17] What kind of failures do you monitor in the SL-DPE testing? (select all that apply)

→ 96% Damage Soft failure  $\rightarrow$  64%

[Q17] Again, we received 53 responses. Pretty much all, 96%, observe damage, while 64% observe soft failures in addition to damage. In order to observe soft failures, the system under test must be powered up and operating. Such a powered system tests cannot be performed on a standalone IC.

Industry Council on ESD Target Levels

## 18. [Q18] Do you rate System Level Direct Pin ESD (SL-DPE) as repeatable?

427 [Q18] All 53 respondents answered this question. Most, 64%, consider SL-DPE to be repeatable.

429

430

432

433 434

435

436

437

438 439

440

441

442

428

426

### 19. [Q019] Which ports are tested?

431 For 'Other', the following answers were given

- LIN (7x)

- Mobile display connector pins

- PCIe

- Special ports

- Input wrist strap and smock, I/O ports

- Global IOs pins for automotive products

- Supply, wake, high side switches, custom interfaces, etc.

- PoE

- 12C

- legacy automotive interfaces (SENT, PSI, LIN), general purpose global IOs, global supply pins

| 443 | - BAT/Wake                            |                                                                         |

|-----|---------------------------------------|-------------------------------------------------------------------------|

| 444 | - all pins of an M                    | CU or MPU                                                               |

| 445 | - <i>PSI5</i>                         |                                                                         |

| 446 | - PSI and other co                    | ustomized inputs and outputs                                            |

| 447 | - RSxxx                               |                                                                         |

| 448 |                                       |                                                                         |

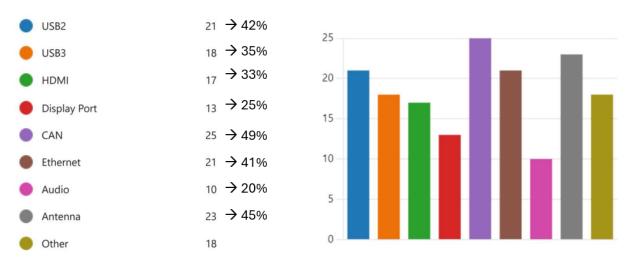

| 449 | [Q19] 51 answers were provi           | ded. Based on these responses, we see a wide range of ports being       |

| 450 | tested. Most of the ports are         | externally accessible by a customer. Testing mainly high-speed and      |

| 451 |                                       | is it is relatively easy to protect low-speed and power connections.    |

| 452 |                                       |                                                                         |

| 453 |                                       |                                                                         |

| 454 |                                       |                                                                         |

|     | 26. [Q26] Have you develo             | ped a test for other pin stress scenarios? (select all that apply)      |

|     | short from VBUS to a data line in USB | 6 → 40%                                                                 |

| 455 | Other                                 | 9 → 60%                                                                 |

| 456 | For 'Other', the followin             | na answers were aiven                                                   |

| 457 | - No (4x)                             | g anomore and green                                                     |

| 458 | - Surge test                          |                                                                         |

| 459 | - Sensor Pins                         |                                                                         |

| 460 |                                       | ve requests to do powered on TLP and powered on VF-TLP and to correlate |

| 461 | -                                     | ailure level (which the two do not correlate but we get these requests  |

| 462 | anyway)                               | andre lever (which the two do not correlate but we get these requests   |

| 463 |                                       | ulse (charged board discharge through IO)                               |

| 464 | •                                     | ment, various non-standard tests are developed on the basis of the      |

| 465 | problem situati                       |                                                                         |

|     | problem situati                       | on ended                                                                |

| 466 | [026] 45                              | ded There's ded Commence of the tenter of a VIDIO short                 |

| 467 |                                       | ded. These included 6 responses referring to a test of a VBUS short     |

| 468 |                                       | sts included powered TLP and surge tests. Besides the USB VBUS          |

| 469 | test, there doesn't appear an         | y broader significance of a specific stress test.                       |

| 470 |                                       |                                                                         |

| 471 |                                       |                                                                         |

| 472 |                                       |                                                                         |

| 473 |                                       |                                                                         |

| 474 |                                       |                                                                         |

| 475 |                                       |                                                                         |

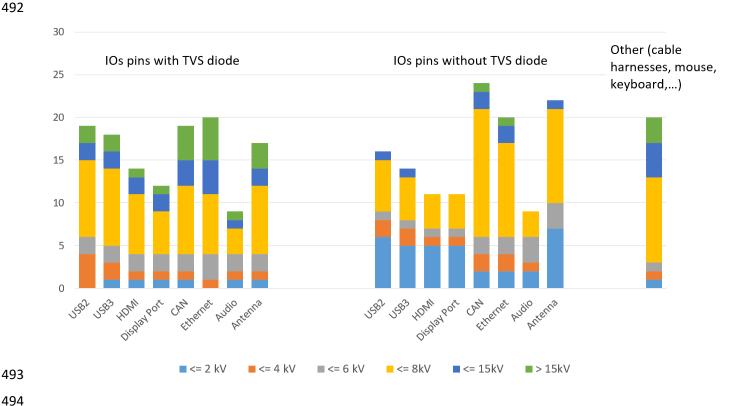

# Chapter 3: Qualification/Testing Targets and Design Goals

**Summary** (the following overview lists observations from different industries and do not constitute recommendations):

- Only 50% of responses provide detailed feedback on targets per interface for system level direct ESD pin testing.

- The reported levels range from 2 kV (or lower) to 15 kV without TVS and from 4 kV to >15 kV with TVS for almost all pin types which connect to a system pin.

- Exceptions are CAN and Ethernet pins where a higher ESD robustness is expected without TVS devices.

- About 40% of the response are reporting correlation between tested robustness and field returns. If there is missing corelation it is mostly attributed to insufficient statistics and lack of information.

- 2/3 of the responses are considering SL-DPE as a design criterion. The design decisions are predominantly based on TLP results.

20. [Q20] What target levels do you apply for each of the following interfaces (contact discharge)?

25

476 477

478 479

480

481

482

483

484 485

486

487

488

489

490

[Q20] Depending on the IO type 18 - 24 answers have been provided ("n/a" responses have been omitted). Not all responses have addressed all types of IOs. It is clearly seen that there is both a lack of test targets, and the targets vary considerably between companies. It is obvious that the largest target group is a goal of 8 kV. This can probably be traced back to the standards like CE where a contact ESD robustness of a system of 8 kV is requested. In these cases, there is no distinction between a chassis part and a port connector, despite the exclusion of the system level direct pin ESD test by IEC 61000-4-2 in case of connectors with grounded shield. Only 7 of the respondents have different target levels for testing w/ and w/o a TVS diode. All 7 of these respondents identify themselves also as system manufacturers.

21. [Q21] Do you also test supply pins for these interfaces?

[Q21] 53 answers have been provided. 29/53 apply system level direct pin ESD stress also to the supply pins.

22. [Q22] Do you see any correlation between the robustness of the pins evaluated by your applied direct pin stress test method and field returns?

[Q22] 50 answers have been provided. From the group of IC suppliers 14/33 (42%) have answered with yes. From the group of non- IC suppliers 8/17 (47%) have confirmed a correlation. Less than half of the companies see a correlation between the robustness of the part evaluated by the type of test they apply and the field returns. Given the complexity of analyzing the correlation across a supply chain in very different industrial domains and markets, it is not surprising that the correlation between the measured robustness and field returns is <50%.

23. [Q23] Can you give details on missing correlation to field returns? (select all that apply)

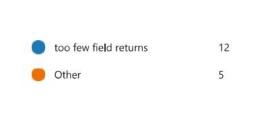

[Q23] 17 answers have been provided. IC suppliers 6/9 (67%) and Non-IC suppliers 6/8 (75%) claim too few field returns to create a meaningful correlation.

For 'Other', the following answers were given

- No detailed FA

- too little information from the field

In some cases, an EOS type field fails were suspected:

- ESD Requirement at good level

- Hard to assess if returned devices damages are due to ESD or EOS

- Customer did not comply with our IC usage guidelines, including power-up sequence, max rating ...etc

24. [Q24] What are the field scenarios for which you observed correlations?

for detailed responses, see [Q24] in Appendix A2

[Q24] 18 answers have been provided. Systems with low ESD robustness as tested in the lab or low-cost systems without ESD protection on the board show higher field return rate. On the contrary, if passing internal system ESD tests, no ESD related field return is seen. Correlation was found to poor ESD

protection methods in the environment or to weak system design. For example, the wiring of IC pins to an exposed part of the system. Hot plugging and cable discharge are also mentioned as discharge scenarios in the field. A Damage of antenna and USB interfaces are explicitly quoted as reasons for field fails.

#### 25. [Q25] What were the criteria for the observed correlations to field returns? (select all that apply)

[Q25] 22 answers have been provided. The question has only addressed the group of responses who are claiming correlation. The response was analysed for IC supplier and non-IC suppliers. Multiple answers were possible (e.g. leakage and system behaviour were considered in the correlation).

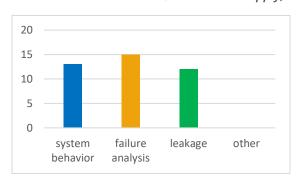

#### IC suppliers

| 553 | • | system behavior  | 10/15 | <b>→</b> 67% |

|-----|---|------------------|-------|--------------|

| 554 | • | failure analysis | 7/15  | <b>→</b> 47% |

| 555 | • | leakage          | 9/15  | <b>→</b> 60% |

| 556 | • | other            | 0/15  | → 0%         |

#### 557 Non-IC suppliers

|     | and the back of the                  | 2 /0 | > 200/ |

|-----|--------------------------------------|------|--------|

| 558 | <ul> <li>system behavior</li> </ul>  | 3/8  | → 38%  |

| 559 | <ul> <li>failure analysis</li> </ul> | 8/8  | → 100% |

| 560 | <ul><li>leakage</li></ul>            | 3/8  | → 38%  |

| 561 | <ul><li>other</li></ul>              | 0/8  | → 0%   |

It is an interesting fact that IC suppliers have a higher focus on system behavior, while non-IC suppliers are basing their judgement on physical failure analysis. Overall, it can be stated that system behavior, failure analysis and leakage testing are considered in the evaluation.

27. [Q27] Do you consider System Level Direct Pin ESD (SL-DPE) as a design criterion for IC design or IO IP design?

567

568

569

[Q27] 49 answers have been provided. 23 of 33 responding with yes are IC suppliers. These are 64% (23/36) of all responses identifying themselves to be IC suppliers (see [Q01]).

570

- 571

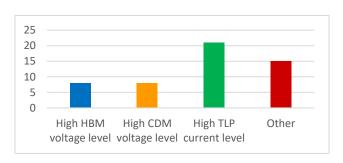

- 28. [Q28] What is the design criterion of the IC interface to achieve high robustness under system level direct pin ESD conditions? Design for ... (select all that apply)

High HBM voltage level  $8 \rightarrow 23\%$ High CDM voltage level  $8 \rightarrow 23\%$ High TLP current level  $21 \rightarrow 60\%$ Other  $15 \rightarrow 43\%$

572573

574

575

576

577578

579

580

581

582

583

584 585

#### For 'Other', the following answers were given

- TLP current target & high TLP Clamp voltage

- Long(er) pulses

- Passing IEC61000-4-2 or ISO 10605 stress

- High IEC 61000-4-2 at IC level

- System ESD stress pulse (with or without PCB components depending on pin category)

- 8kV pass with IEC gun on IC outside the system

- Residual current on chip as expected from SEED simulation with application; expected transient voltage at pin under test and supply and GND

- PESD direct pin discharge

- Direct application of HMM

- Appropriate optimization with SEED

- Simulations